Matrix Multiplication Through Systolic Array: Fall 2019

Summary

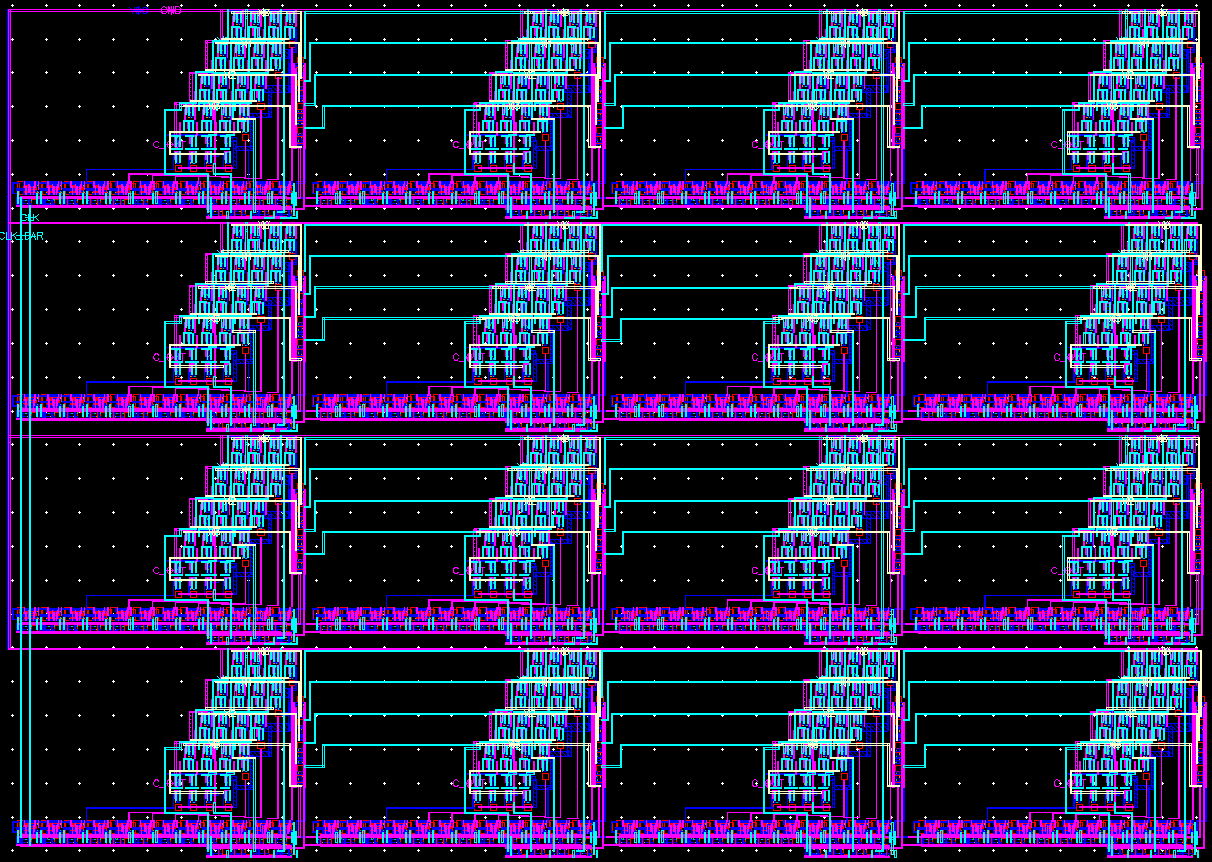

We developed a systolic to perform matrix multiplication on 4x4 matrices consisting of 4-bit numbers in this work. Due to the complexity of the circuit, we broke the system down into simple components and tested them separately. We constructed DPUs from CSA units, full adders, and flip-flops, and then the DPUs were used to construct the systolic array. After initial testing, we laid out the circuit as shown in figure 1. While each of the individual components of the systolic array was minimally sized, the overall size of the circuit was large because of sizable areas of unused space. This was because different students individually laid out the components of the circuits without thoroughly considering how they would fit together. If given more time, we would have liked to revisit the layouts of the individual components to reduce the die area.

Figure 1: Layout of the Systolic Array

Through this project, I gained experience in using Cadence Virtuoso to design and simulate digital circuits. I also learned how to build complex digital circuits from simple building blocks through hierarchical design. The biggest lesson that I learned from this project was the importance of designing each component to not only use a minimal amount of space independently but also when combined with other components.